The MPC9315 is a 2.5V and 3.3V compatible phase-locked loop based clock generator designed for low-tilt clock distribution in low-voltage mid-range to high performance telecommunications, networking and computing applications.

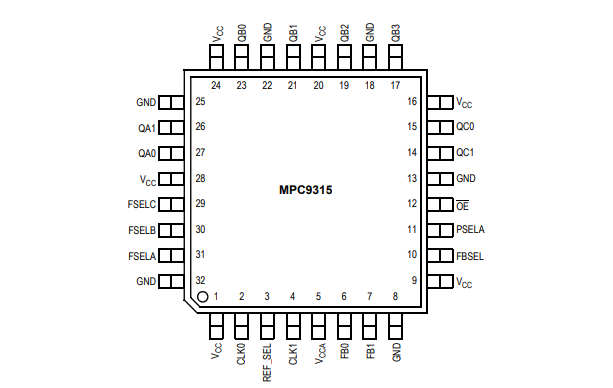

32-Lead Package Pinout (Top View)

The MPC9315 offers eight low-tilt outputs and two optional clock redundancy inputs. Output can be configured to support 1:1,2:1,4:1,1:2 and 1:4 output/input frequency ratios. In addition, the selectable output 180° phase control supports advanced clock schemes with backclock signals. The extended temperature range specified by MPC9315 is n40 to +85°C

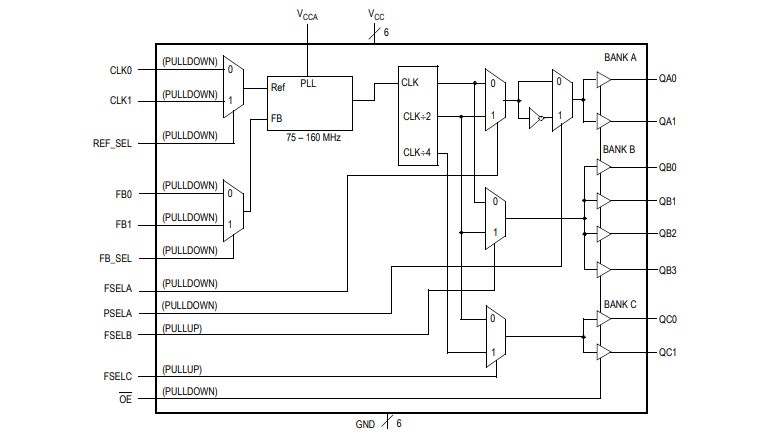

Logic Diagram